昆明聯誠科技作為一家專注于信息技術領域的企業,提供多元化的技術集成服務,涵蓋開放式收費軟件、計算機網絡信息系統集成、工業自動控制系統、閉路電視監控系統工程、管理信息系統以及辦公自動化等多個方面。這些服務旨在幫助客戶提升運營效率、優化資源配置,并實現智能化管理。

在開放式收費軟件方面,昆明聯誠科技開發了靈活的解決方案,適用于交通、停車、公共服務等領域。該軟件支持多種支付方式,如現金、移動支付和刷卡,確保收費過程高效、透明,同時降低了人為錯誤。通過模塊化設計,客戶可根據實際需求進行定制,適應不同業務場景的變化。

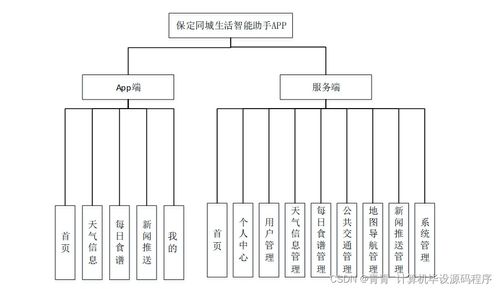

計算機網絡信息系統集成是昆明聯誠科技的核心業務之一。公司致力于為客戶搭建穩定、安全的網絡架構,結合云計算和大數據技術,實現數據的無縫傳輸與共享。這不僅提升了企業的通信效率,還保障了信息系統的可靠性和可擴展性,適用于企業、政府機構及教育單位。

工業自動控制系統則聚焦于制造業和流程工業,昆明聯誠科技通過集成PLC、SCADA等技術,實現生產線的自動化控制。這有助于減少人工干預,提高生產精度和效率,同時降低運營成本。系統支持遠程監控和故障診斷,確保工業流程的連續性和安全性。

閉路電視監控系統工程提供全面的安防解決方案,昆明聯誠科技采用高清攝像頭、智能分析軟件和網絡存儲技術,構建起覆蓋廣泛的監控網絡。該系統不僅用于實時監視,還具備報警和錄像功能,適用于公共場所、企業和住宅區,有效防范安全風險。

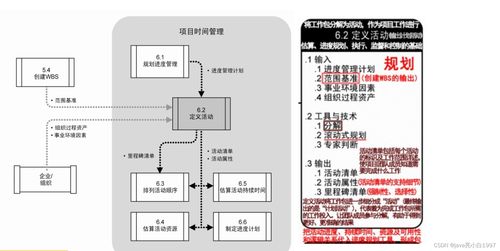

管理信息系統是昆明聯誠科技的另一個重點領域,通過整合ERP、CRM等軟件,幫助企業管理資源、客戶關系和業務流程。系統提供數據分析報告,輔助決策者制定戰略,提升整體管理水平。

辦公自動化方面,昆明聯誠科技推廣智能辦公解決方案,包括文檔管理、協同辦公平臺和自動化流程工具。這顯著提高了員工的工作效率,減少了紙質文件的使用,符合綠色環保理念。

總體而言,昆明聯誠科技以開放式收費軟件為起點,結合多領域技術集成,為客戶提供全面的數字化服務。這些解決方案不僅推動了企業的信息化轉型,還促進了社會經濟的智能化發展。未來,隨著技術的不斷進步,昆明聯誠科技將繼續創新,為更多行業帶來高效、可靠的系統集成服務。