隨著信息技術(shù)的快速發(fā)展,商品管理系統(tǒng)在現(xiàn)代商業(yè)運(yùn)作中扮演著至關(guān)重要的角色。本文詳細(xì)介紹了一個(gè)基于PHP和MySQL技術(shù)的商品管理系統(tǒng),該系統(tǒng)作為計(jì)算機(jī)專業(yè)畢業(yè)設(shè)計(jì)的完整解決方案,編號(hào)19895,充分體現(xiàn)了計(jì)算機(jī)系統(tǒng)集成的核心思想。

一、系統(tǒng)概述

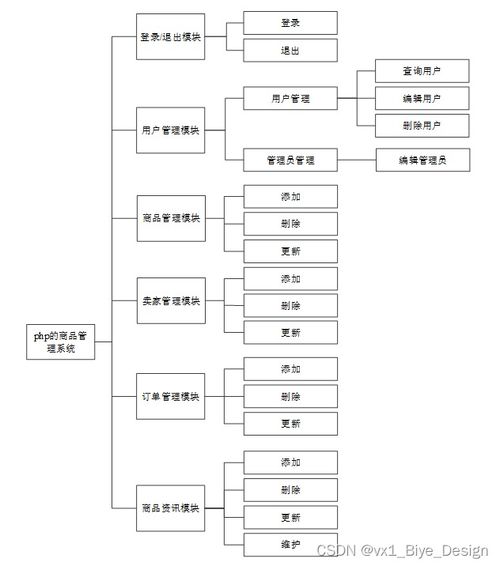

本商品管理系統(tǒng)采用B/S架構(gòu),前端使用HTML、CSS和JavaScript技術(shù),后端采用PHP編程語(yǔ)言,數(shù)據(jù)庫(kù)選用MySQL。系統(tǒng)實(shí)現(xiàn)了商品信息管理、庫(kù)存管理、銷售管理、用戶管理等核心功能模塊,為企業(yè)提供了一套完整的商品管理解決方案。

二、系統(tǒng)架構(gòu)設(shè)計(jì)

系統(tǒng)采用典型的三層架構(gòu)模式:

- 表示層:負(fù)責(zé)用戶界面展示和交互

- 業(yè)務(wù)邏輯層:處理系統(tǒng)核心業(yè)務(wù)邏輯

- 數(shù)據(jù)訪問(wèn)層:負(fù)責(zé)與MySQL數(shù)據(jù)庫(kù)的交互操作

這種分層架構(gòu)確保了系統(tǒng)的可維護(hù)性和可擴(kuò)展性,符合計(jì)算機(jī)系統(tǒng)集成的設(shè)計(jì)原則。

三、數(shù)據(jù)庫(kù)設(shè)計(jì)

MySQL數(shù)據(jù)庫(kù)設(shè)計(jì)包含以下主要數(shù)據(jù)表:

- 商品信息表(product_info):存儲(chǔ)商品基本信息

- 庫(kù)存表(inventory):記錄商品庫(kù)存數(shù)量

- 銷售記錄表(sales_record):保存銷售流水

- 用戶表(user):管理系統(tǒng)用戶信息

- 分類表(category):商品分類信息

數(shù)據(jù)庫(kù)表之間通過(guò)外鍵建立關(guān)聯(lián),確保數(shù)據(jù)的一致性和完整性。

四、核心功能模塊

- 商品管理模塊

- 商品信息錄入與編輯

- 商品分類管理

- 商品查詢與篩選

- 商品圖片上傳功能

- 庫(kù)存管理模塊

- 庫(kù)存數(shù)量實(shí)時(shí)更新

- 庫(kù)存預(yù)警功能

- 入庫(kù)/出庫(kù)記錄管理

- 庫(kù)存盤點(diǎn)功能

- 銷售管理模塊

- 銷售訂單創(chuàng)建

- 銷售統(tǒng)計(jì)分析

- 銷售報(bào)表生成

- 客戶信息管理

- 系統(tǒng)管理模塊

- 用戶權(quán)限管理

- 系統(tǒng)日志記錄

- 數(shù)據(jù)備份與恢復(fù)

- 系統(tǒng)參數(shù)設(shè)置

五、技術(shù)特點(diǎn)與創(chuàng)新

- 采用PDO數(shù)據(jù)庫(kù)連接方式,提高系統(tǒng)安全性

- 實(shí)現(xiàn)Ajax異步交互,提升用戶體驗(yàn)

- 加入數(shù)據(jù)驗(yàn)證機(jī)制,確保數(shù)據(jù)的準(zhǔn)確性

- 采用MVC設(shè)計(jì)模式,代碼結(jié)構(gòu)清晰

- 實(shí)現(xiàn)權(quán)限分級(jí)管理,保障系統(tǒng)安全

六、系統(tǒng)實(shí)現(xiàn)效果

經(jīng)過(guò)測(cè)試,系統(tǒng)運(yùn)行穩(wěn)定,界面友好,操作簡(jiǎn)便。系統(tǒng)能夠有效提高商品管理效率,減少人工錯(cuò)誤,為企業(yè)決策提供準(zhǔn)確的數(shù)據(jù)支持。系統(tǒng)響應(yīng)速度快,在并發(fā)用戶數(shù)較多的情況下仍能保持良好的性能表現(xiàn)。

七、總結(jié)與展望

本系統(tǒng)作為計(jì)算機(jī)畢業(yè)設(shè)計(jì)項(xiàng)目,完整實(shí)現(xiàn)了商品管理的基本需求,體現(xiàn)了PHP和MySQL技術(shù)在Web開(kāi)發(fā)中的優(yōu)勢(shì)。未來(lái)可以考慮加入更多智能化功能,如銷售預(yù)測(cè)、智能補(bǔ)貨提醒等,進(jìn)一步提升系統(tǒng)的實(shí)用價(jià)值。